CSE 506: Operating Systems

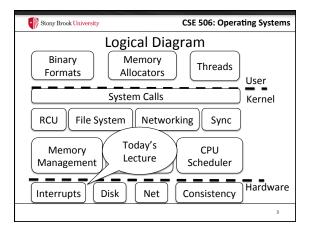

Lecture outline

Overview

How interrupts work in hardware

How interrupt handlers work in software

How system calls work

New system call hardware on x86

CSE 506: Operating Systems

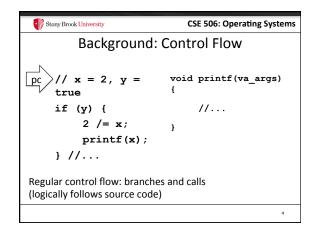

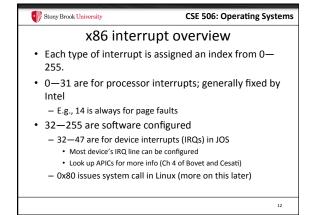

Interrupt overview

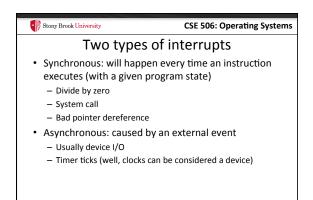

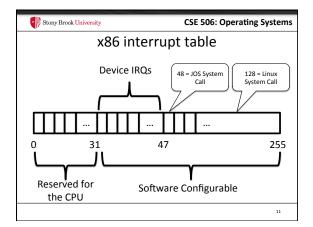

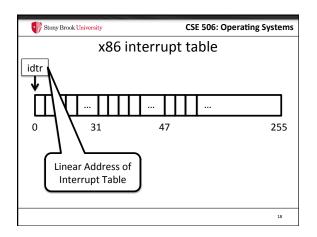

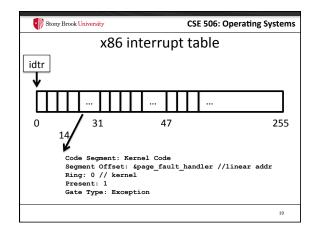

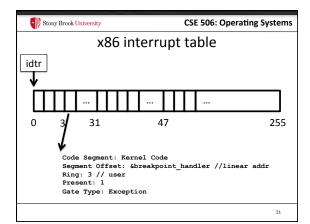

Each interrupt or exception includes a number indicating its type

E.g., 14 is a page fault, 3 is a debug breakpoint

This number is the index into an interrupt table

CSE 506: Operating Systems

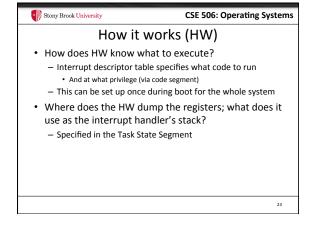

What happens (generally):

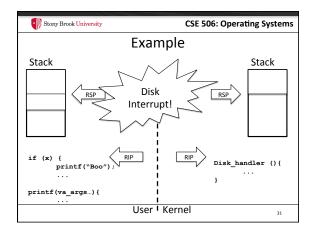

Control jumps to the kernel

At a prescribed address (the interrupt handler)

The register state of the program is dumped on the kernel's stack

Sometimes, extra info is loaded into CPU registers

E.g., page faults store the address that caused the fault in the cr2 register

Kernel code runs and handles the interrupt

When handler completes, resume program (see iret instr.)

\*\*Stony Brook University\*\*

\*\*CSE 506: Operating Systems\*\*

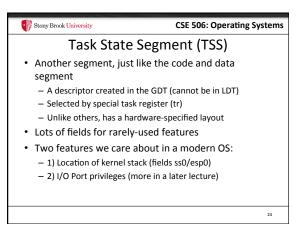

\*\*How is this configured?\*

\*\*Kernel creates an array of Interrupt descriptors in memory, called Interrupt Descriptor Table, or IDT

- Can be anywhere in memory

- Pointed to by special register (idtr)

\*\*c.f., segment registers and gdtr and ldtr\*

\*\*Entry 0 configures interrupt 0, and so on

CSE 506: Operating Systems

Hardware interrupt sync.

While a CPU is servicing an interrupt on a given IRQ line, the same IRQ won't raise another interrupt until the routine completes

Bottom-line: device interrupt handler doesn't have to worry about being interrupted by itself

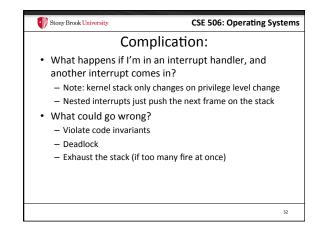

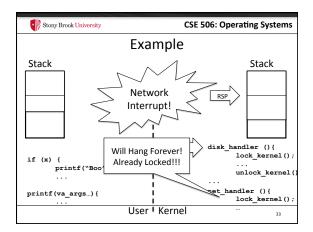

A different device can interrupt the handler

Problematic if they share data structures

Like a list of free physical pages...

What if both try to grab a lock for the free list?

CSE 506: Operating Systems

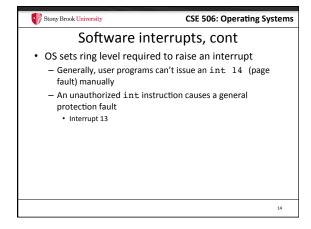

Disabling interrupts

• An x86 CPU can disable I/O interrupts

— Clear bit 9 of the EFLAGS register (IF Flag)

— cli and sti instructions clear and set this flag

• Before touching a shared data structure (or grabbing a lock), an interrupt handler should disable I/O interrupts

**CSE 506: Operating Systems**

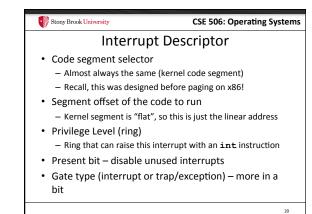

## Gate types

- Recall: an IDT entry can be an interrupt or an exception gate

- · Difference?

- An interrupt gate automatically disables all other interrupts (i.e., clears and sets IF on enter/exit)

- An exception gate doesn't

- This is just a programmer convenience: you could do the same thing in software

37

**CSE 506: Operating Systems**

### Exceptions

- You can't mask exceptions

- Why not?

- Can't make progress after a divide-by-zero

- Double and Triple faults detect faults in the kernel

- Do exception handlers need to be reentrant?

- Not if your kernel has no bugs (or system calls in itself)

- In certain cases, Linux allows nested page faults

- E.g., to detect errors copying user-provided buffers

38

**CSE 506: Operating Systems**

## Summary

- Interrupt handlers need to synchronize, both with locks (multi-processor) and by disabling interrupts (same CPU)

- Exception handlers can't be masked

- Nested exceptions generally avoided

39

Stony Brook University

CSE 506: Operating Systems

### Lecture outline

- Overview

- · How interrupts work in hardware

- · How interrupt handlers work in software

- · How system calls work

- New system call hardware on x86

4

CSE 506: Operating Systems

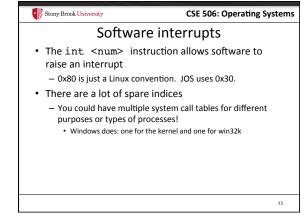

# System call "interrupt"

- Originally, system calls issued using int instruction

- Dispatch routine was just an interrupt handler

- Like interrupts, system calls are arranged in a table

- See arch/x86/kernel/syscall\_table\*.S in Linux source

- Program selects the one it wants by placing index in eax register

- Arguments go in the other registers by calling convention

- Return value goes in eax

41

Stony Brook University

**CSE 506: Operating Systems**

## Lecture outline

- Overview

- How interrupts work in hardware

- How interrupt handlers work in software

- How system calls work

- New system call hardware on x86

42

CSE 506: Operating Systems

### Around P4 era...

- · Processors got very deeply pipelined

- Pipeline stalls/flushes became very expensive

- Cache misses can cause pipeline stalls

- System calls took twice as long from P3 to P4

- Why?

- IDT entry may not be in the cache

- Different permissions constrain instruction reordering

43

Stony Brook University

**CSE 506: Operating Systems**

#### Idea

- What if we cache the IDT entry for a system call in a special CPU register?

- No more cache misses for the IDT!

- Maybe we can also do more optimizations

- Assumption: system calls are frequent enough to be worth the transistor budget to implement this

- What else could you do with extra transistors that helps performance?

44

Stony Brook University

CSE 506: Operating Systems

# AMD: syscall/sysret

- These instructions use MSRs (machine specific registers) to store:

- Syscall entry point and code segment

- Kernel stack

- A drop-in replacement for int 0x80

- Everyone loved it and adopted it wholesale

- Even Intel!

45

Stony Brook University

CSE 506: Operating Systems

### Aftermath

- Getpid() on my desktop machine (recent AMD 6core):

- Int 80: 371 cycles

- Syscall: 231 cycles

- So system calls are definitely faster as a result!

4

Stony Brook University

CSE 506: Operating Systems

### In JOS

- You will use the int instruction to implement system

calls

- There is a challenge problem in lab 3 (i.e., extra credit) to use systenter/sysexit

- Note that there are some more details about register saving to deal with

- Syscall/sysret is a bit too trivial for extra credit

- But still cool if you get it working!

47

Stony Brook University

**CSE 506: Operating Systems**

# Summary

- · Interrupt handlers are specified in the IDT

- Understand when nested interrupts can happen

- And how to prevent them when unsafe

- Understand optimized system call instructions

- Be able to explain syscall vs. int 80

48